| 产品分类 |

| 电源适配器 |

| 手机充电器 |

电话:+86 0511-86482222

传真:+86 0511-86612939

网址: www.yamahui.com

邮箱:chenyang@www.yamahui.com

-

供职器电源微电脑直流高压器程控测试电源程控电源

发布日期:2025-04-30 07:55:32 来源:竞技宝入口官网首页 作者:竞技宝平台官方台积电 2025 年北美时间论坛不只发表了最先辈的A14 逻辑造程,正在先辈封装界限也有多项首要消息发表。

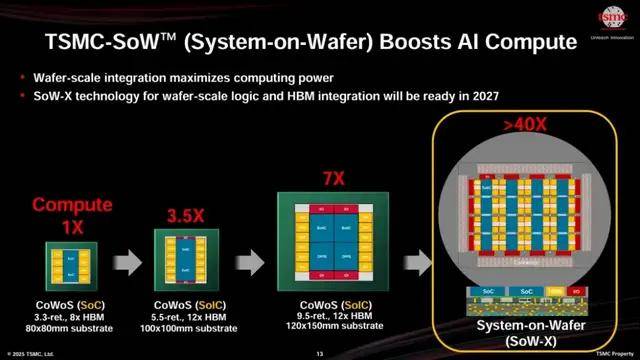

台积电吐露该企业打算正在2027 年量产 9.5 倍光罩尺寸的 CoWoS,从而可能以台积电先辈逻辑时间将 12 个或更多的 HBM 堆叠整合到一个封装中,这意味着单封装可容纳的芯局部积将相较此行进一步提拔。

而正在更大的晶圆尺寸封装体系方面,台积电则带来了SoW 体系级晶圆时间的新版本 SoW-X。该时间采用差异于 SoW-P 的 Chip-Last 流程,打算于 2027 年量产。

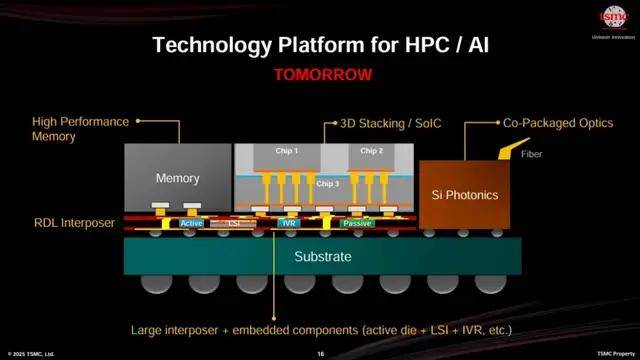

台积还先容了其它一系列高本能集成处分计划,包罗用于HBM4 的 N12 和N3 造程逻辑根底裸晶(Base Die)、使用 COUPE 紧凑型通用光子引擎时间的 SiPh 硅光子整合。

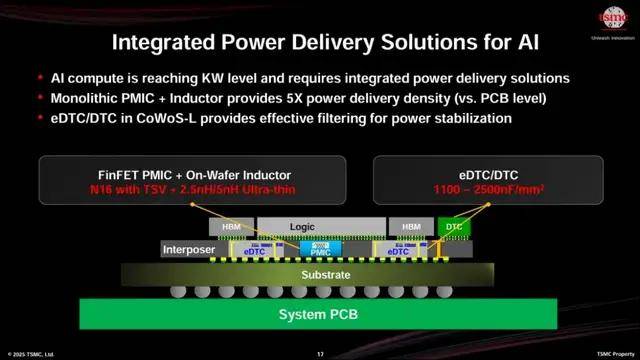

其它台积电也发表了用于 AI 的新型集成型电压调剂器 / 稳压器 IVR。与电途板上的独立电源料理芯片 PMIC 比拟,IVR 具备 5 倍的笔直功率密度传输。

自2020年以后,台积电的晶圆体系集成时间(InFO-SoW)已得胜操纵于如Cerebras和特斯拉等公司的尖端产物中,个中特斯拉的Dojo超等谋划机所搭载的晶圆级解决器便是这一时间的标识性产品。晶圆级计划通过直接正在整片硅晶圆上修建解决器,实行了空前未有的重心间通讯速率、本能密度以及能效,然而,其庞文雅与本钱也相应添加,节造了广博操纵。

面临人为智能(AI)与高本能谋划(HPC)界限日益增加的需求,纯洁的二维扩展已无法知足。台积电通过统一其InFO-SoW与集成芯片体系(SoIC)两大封装时间,推出了CoW-SoW时间,旨正在实行晶圆级芯片的笔直堆叠。这项时间不只允诺逻辑芯片与内存芯片正在统一晶圆长举行堆叠,还供给了空前未有的天真性,使得差异筑造工艺时间可能正在统一封装内共存,从而优化本钱效益与本能展现。

尤其是正在内存集成方面,台积电尤其夸大了CoW-SoW正在贯串HBM4(第四代高带宽内存)上的潜力。HBM4仰仗其2048位的超宽接口,希望通过与逻辑芯片的紧茂密成,处分AI及HPC任务负载对高带宽、低延迟内存的火急需求。这种集成办法不只极大提拔了数据传输速率,再有用下降了功耗,为接续增加的谋划茂密型操纵供给了理念的处分计划。

台积电营业拓荒副总裁Kevin Zhang正在研讨会中表达了对CoW-SoW时间的果断信念,以为它将成为客户提拔AI集群或超等谋划机本能的合头途途。他夸大,晶圆级集成不只不再是表面设念,而是正正在与客户团结转化为实质产物,标识着台积电正引颈行业向更高宗旨的体系集成迈进。

本年3月SK海力士揭橥,推出头向AI的超高本能DRAM新产物12层HBM4,而且环球初度向厉重客户供给了其样品。SK海力士夸大:“以引颈HBM市集的时间逐鹿力和分娩经历为根底,可能比原打算提早实行12层HBM4的样品出货,并已劈头与客户的验证流程。公司将鄙人半年告终量产绸缪,由此稳定正在面向AI的新一代存储器市集教导身分。”

此次供给的12层HBM4样品,兼具了面向AI的存储器必备的宇宙最高程度速度。其容量也是12层堆叠产物的最高程度。

此产物初度实行了最高每秒可能解决2TB(太字节)以上数据的带宽1。其相当于正在1秒内可解决400部以上全高清(Full-HD,FHD)级片子(5GB=5千兆字节)的数据,运转速率与前一代(HBM3E)比拟降低了60%以上。

同时,公司通过正在该产物上采用已正在前一代产物得回逐鹿力承认的Advanced MR-MUF工艺,实行了现有12层HBM可抵达的最大36GB容量。通过此工艺负责了芯片的翘曲情景,再有用提拔了散热本能,由此最大水准地降低了产物的安祥性。

SK海力士从2022年的HBM3劈头,正在2024年连续实行了8层和12层HBM3E产物量产,通过恰时拓荒和供应HBM产物,庇护了面向AI的存储器市集教导力。

SK海力士AI Infra继承金柱善社长(CMO,Chief Marketing Officer)吐露:“公司为了知足客户的央求,不绝取胜时间限度,成为了AI生态改进的当先者。以业界最大界限的HBM供应经历为根底,以后也将利市举行本能验证和量产绸缪。”